ZeroPoint Technologies AB, a Swedish startup business showing up as a spinout of the Chalmers College of Technological know-how, has these days announced its hottest get the job done. Ziptilion, a memory technology that has been awarded a patent, €2.5 million (just under $3 million) in seed funding, and guarantees to double your RAM capacity and bandwidth, all although attaining higher energy effectiveness.

Many of you don’t forget the old RAM doubling computer software that existed back again in the 80s and 90s. They have been a significant scam at the time, promising customers who acquired the application double their ram capacities without having a proper hardware upgrade. Currently, ZeroPoint designs to do that, on the other hand, with a entirely diverse, components-based mostly strategy.

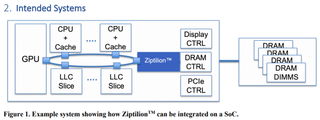

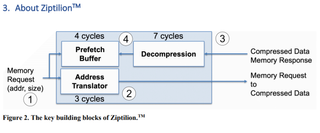

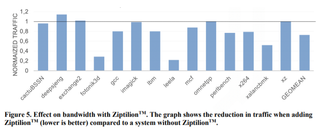

Referred to as the Ziptilion, this hardware IP works by compressing memory knowledge applying proprietary compression algorithms, and ZeroPoint claims an2-3 occasions increase in bandwidth. The way Ziptilion operates is by embedding the IP into a style and design, and it is effective straight with a memory controller and processor’s cache subsystem, employing the industry-common SoC AXI interconnect cloth. The corporation claims that its engineering can compress memory in this kind of an productive way that memory latency typically is lessened by utilizing the Ziptilion IP, as it fetches the compressed info from and to the memory. In extreme scenarios, the latency can be larger somewhere around 1-100 nanoseconds, having said that, the gains are outweighing the downsides.

And you may possibly po

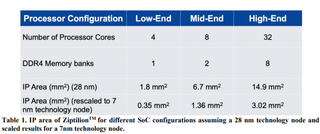

nder what is the price of this IP? Properly, in accordance to the enterprise, there exists a structure on TSMC’s 28nm node that applied the Ziptilion IP on the AXI bus managing at 800 MHz frequency and with a bandwidth of 32 GB/s. The regular 7 nm twin-channel memory structure that works by using this IP will achieve only 1.36 square millimeters of more die usage, while a server CPU with an 8-channel memory controller will need further 3.02 square millimeters for embedding it.

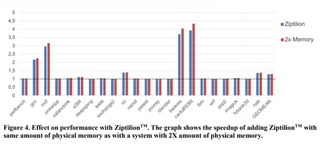

In phrases of performance, the Ziptilion IP whitepaper has in comparison its compression engineering with the addition of a lot more RAM. Precisely, the whitepaper as opposed the effects of doubling the system’s RAM potential with an addition of Ziptilion style to the SoC. It concludes that the new engineering can convey pretty similar effects, correctly doubling your doing work ram ability thanks to the compressed facts.

And for probable programs, the design can be executed in several types. Extra particularly, a SoC like the just one observed on Raspberry Pi and the smartphone SoCs can advantage considerably from it, as these techniques are restricted by the program memory they are equipped with. A straightforward smartphone with 8 GB of RAM could see a increase up to 16 GB RAM with this IP block, as an illustration.

When we really don’t know if this engineering will at any time make it to the mainstream market, it does demonstrate promise, not like the RAM doublers of yesteryear. The individuals guiding the technological innovation have been studying memory compression algorithms for about 15 decades, and it looks like the market place is at last ready for one thing like this to be embedded into future styles.

More Stories

How News Technology is Shaping Public Opinion

Exploring Ethics in News Technology Practices

News Technology: Enhancing Audience Engagement